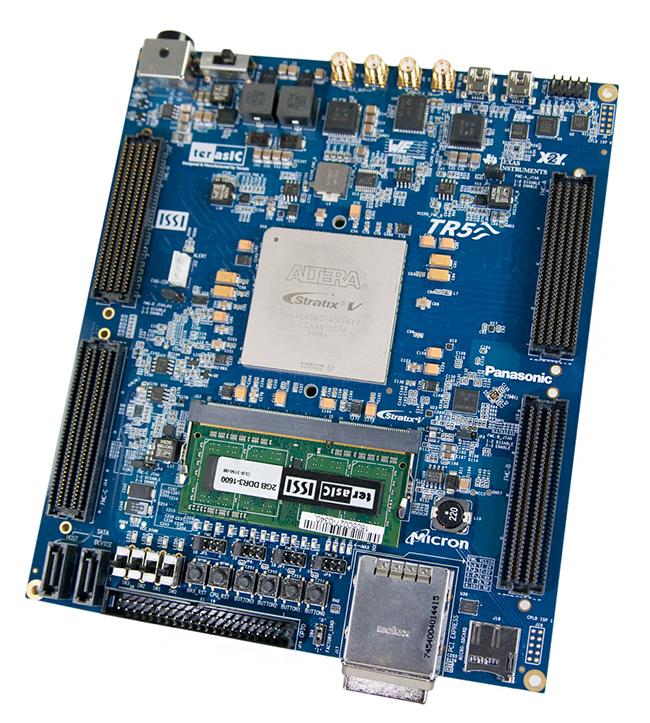

TR5 开发板采用 Altera Stratix V GX FPGA,能提供最多达 622K LE 容量,并进行高速运算及传输。

TR5 开发板采用 Altera Stratix V GX FPGA,能提供最多达 622K LE 容量,并进行高速运算及传输。

TR5 开发板还提供了四个 Fpga Mezzanine Card (FMC) 以及一个 2x20 GPIO 接头。这些连接器总共能提供多达 500 根使用者自订义的 FPGA I/O 并作扩展口来连接外设。搭配 DDR3 SODIMM 和 SSRAM 能为大量数据资料处理提供高速与大量的频宽。除此之外 TR5上 还有 PCIe 与 SATA 介面可供作高速资料传输应用。

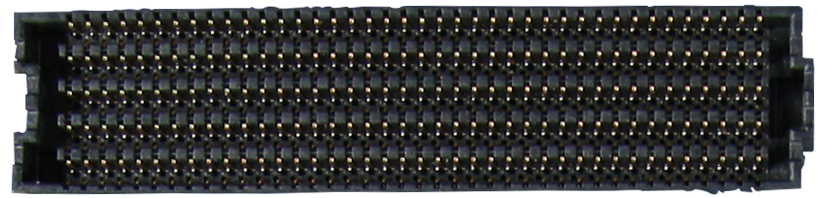

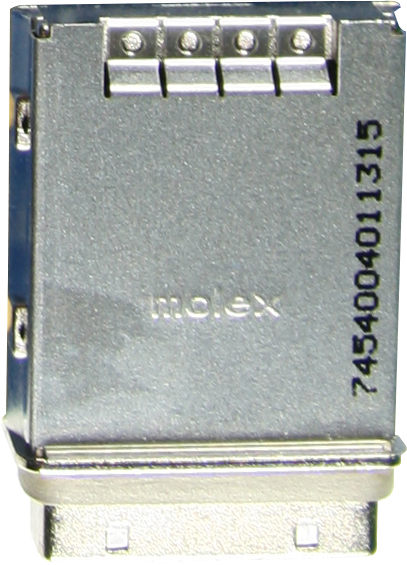

Four FMC connectors

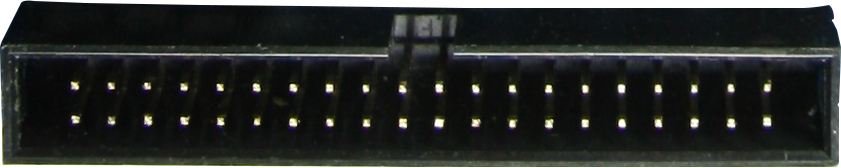

2x20 GPIO connector

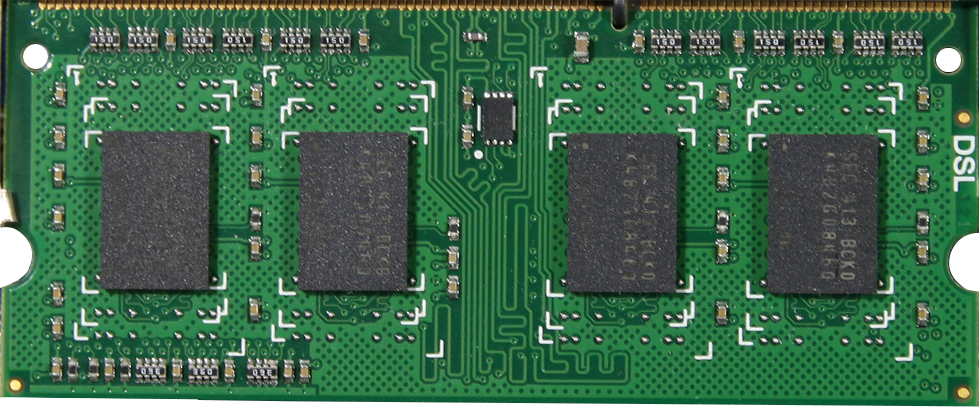

DDR3 memory

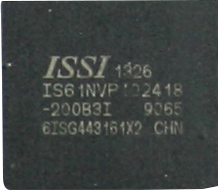

SSRAM

PCIe

SATA

TR5 开发板最多的应用在于 ASIC prototyping 验证。板上的 FMC 接头为标准介面。使用者可以透过此接头连接各种不同介面的子卡来扩展自己的系统。若有需要多片 FPGA 主板组成更庞大系统的客户亦可使用 FMC 或 PCIe 连接线来进行多片 TR5 板的传输来达成目标。

TR5 开发套件包含了许多不同外设的范例,如 DDR3,SD Card,USB-to-UART,SATA,PCIe,及 FMC 介面。这些范例能帮助使用者快速的上手使用还可用来快速验证开发板介面功能。除此之外,还提供了「System Builder」软体工具。让使用者能快速的依照自身的外设需求产生 Qaurtus 顶层专案,包含了 PLL 控制 IP,不同的 Terasic FMC 子卡介面等等.帮助使用者能更快并无误的开始您的专案。