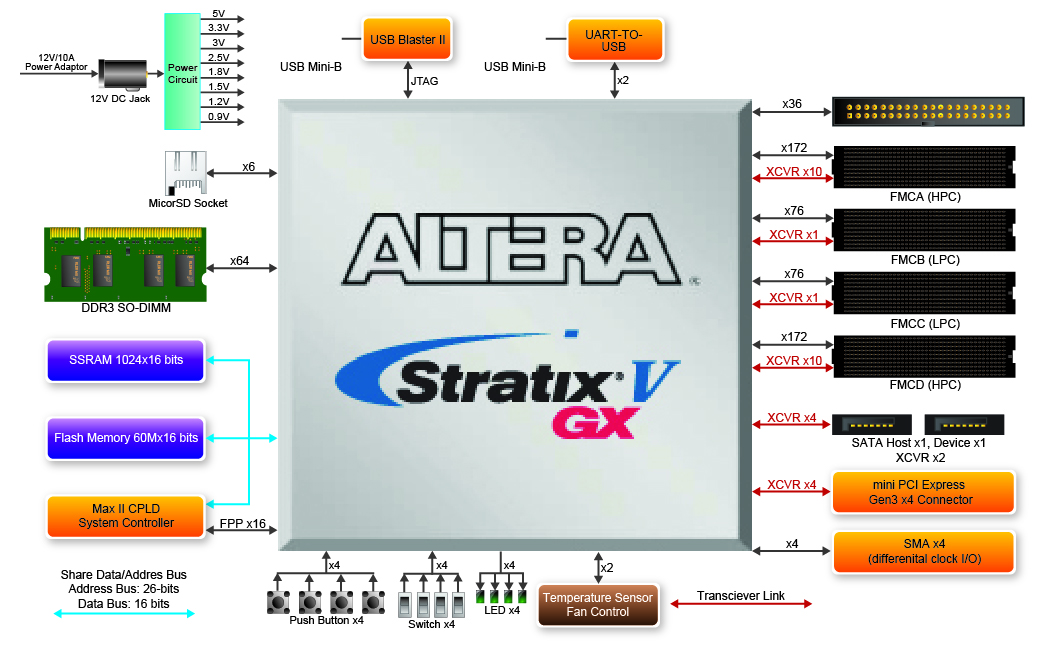

FPGA Device

5SGXEA7N2F45C2N

- 622K Logic Elements (LEs)

- 57.16 Mbits 内存

- 256 Variable-precision DSP Blocks

- 512 18x18-bit Multipliers Blocks

- 28 Fractional PLLs and 4DLLs

- FPGA 亦有其他规格可供选择,详细信息欢迎洽询 Terasic 销售团队。

FPGA 配置

- 板载 USB Blaster II 或 JTAG 插口对 FPGA 编程

- 通过 MAX II CPLD 和 Flash 配置快速被动平行 (FPPx16) 模式

存储器

- 128MB Flash with a 16-bit Data Bus

- 2MB SSRAM (1M x 16)

DDR3 SO-DIMM 插槽

- 可支持多达 8GB

- 最大时钟频率可到 933 MHz

板载时钟

- 50MHz 晶振

- CDCM6208 可编程时钟发生器

- LMK04906B 可编程时钟发生器

SMA 介面

- 一对可用来作差分时钟输入与输出的 SMA 介面

Buttons, Switches and LEDs

- 4 使用者控制 LEDs

- 4 按钮

- 4 拨码开关

PCI Express Gen 3x4 介面

- 支持 PCI Express Gene x4 (8.0Gbps/lanes)

- 高速传输信道速率可达 8 Gbps

- 支持 Downstream Mode

2 个 SATA 介面

- 符合 SATA3.0 传输率 6Gbps

4 个 FPGA Mezzanine Card (FMC) 介面

- 2个 HPC (high-pin count) FMC 介面可提供 172 x2 单端 I/O, 2个 LPC (low-pin count) FMC 介面可提供 76 x2 单端 I/O

- HPC FMC 以及 LPC FMC 介面分别能提供 10 以及 1 根 Transceiver 通道

- 相容于FMC VITA 57.1 规范

- 可调整 VADJ电压 : 1.2V/1.5V/1.8V/2.5V/3.0V

- 无法支持双向LVDS功能, 由于Stratix V只支持单向LVDS.

一 个 40-pin 扩充介面

- 36 FPGA I/O 管脚; 4个电源以及接地线

- I/O 电压准位: 3.3V

电源

- DC 12V 输入

功能区块图

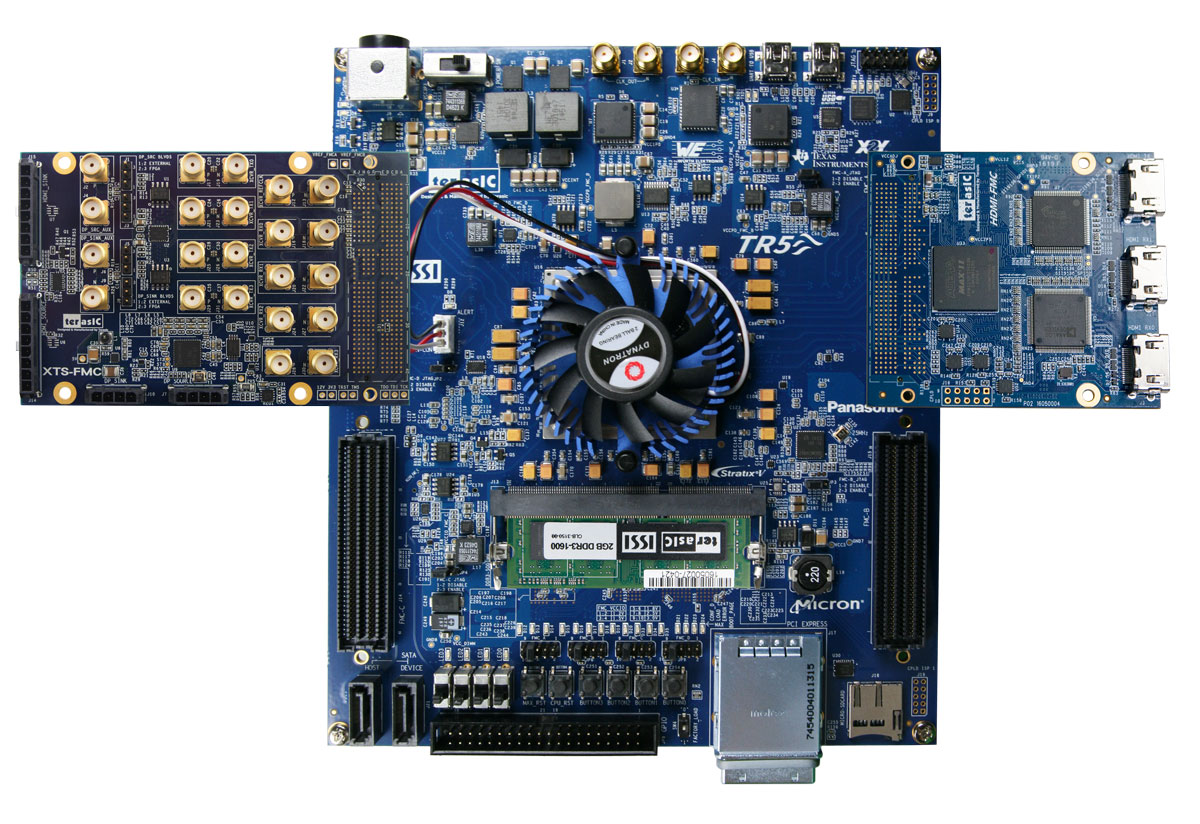

FMC扩充介面连接范例

连接FMC子卡:XTS-FMC 和 HDMI-FMC

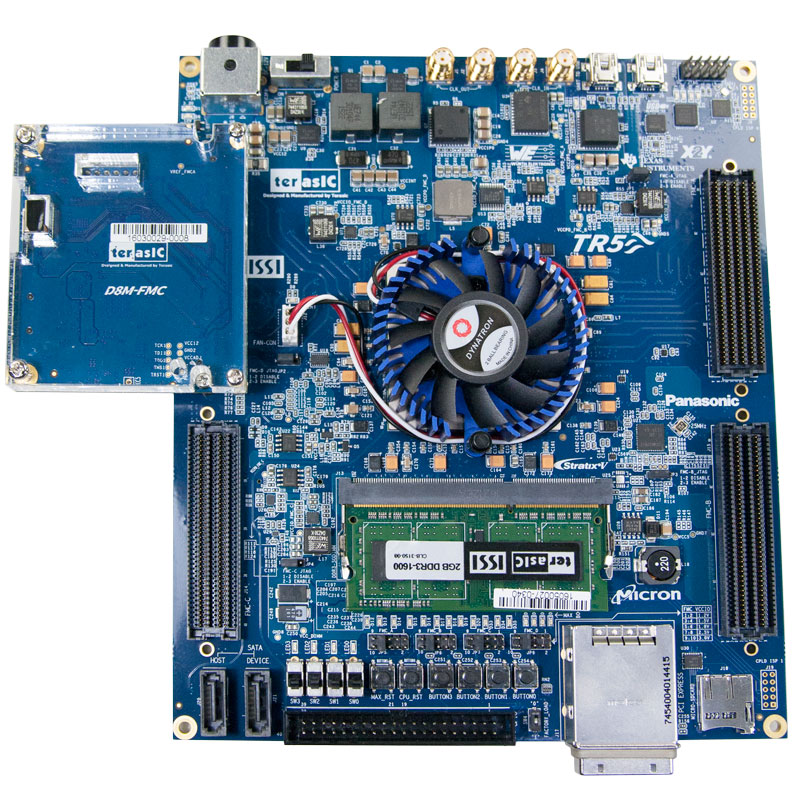

连接 D8M-FMC FMC 子卡

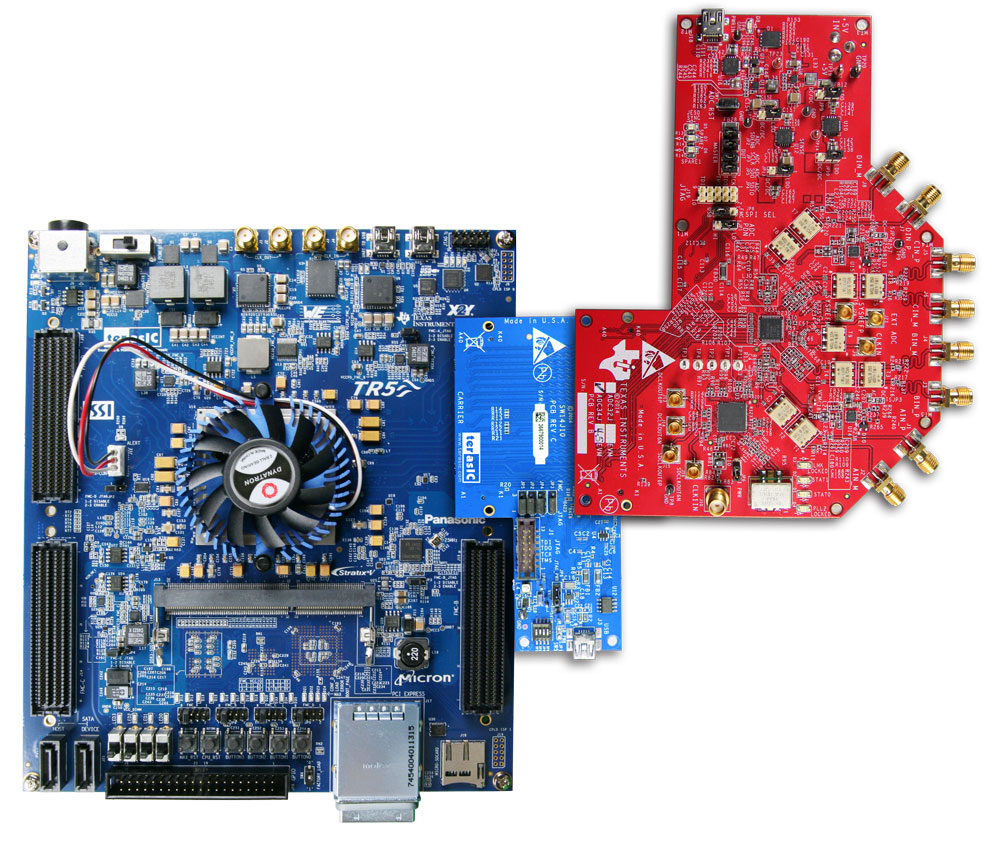

连接 TI JESD 板透过 Terasic JESD-FMC 转接卡

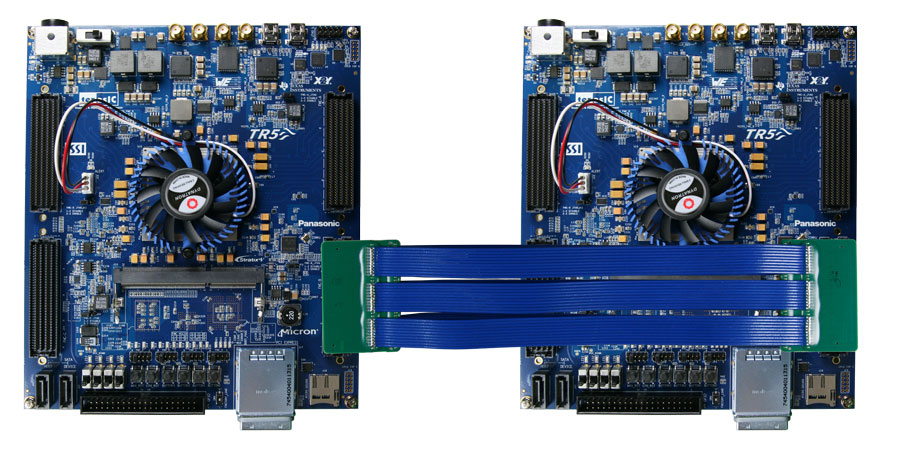

板跟板连接透过 FMC 连接线

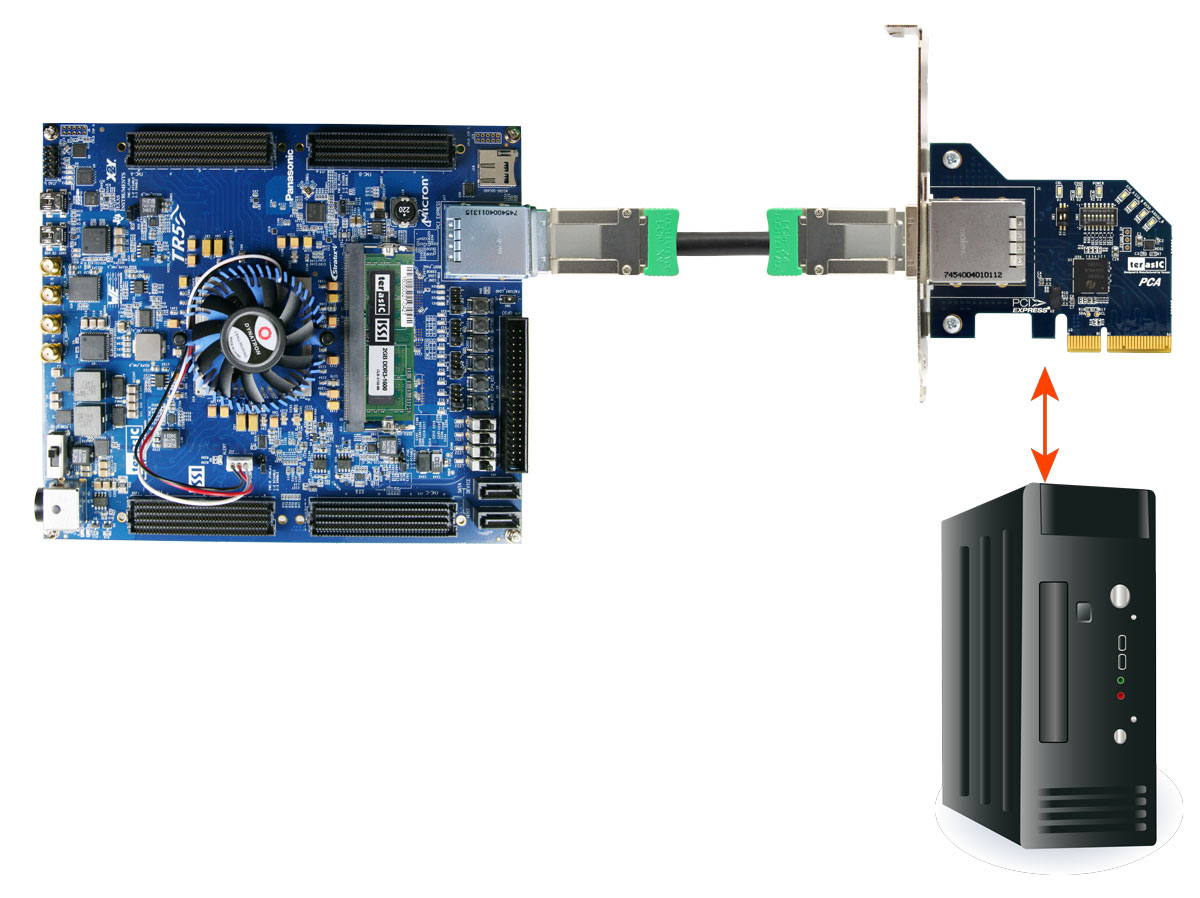

透过 PCI Express 连介面扩充

透过 PCIE连接线 与 Terasic PCA转接卡 来与 PC 连接

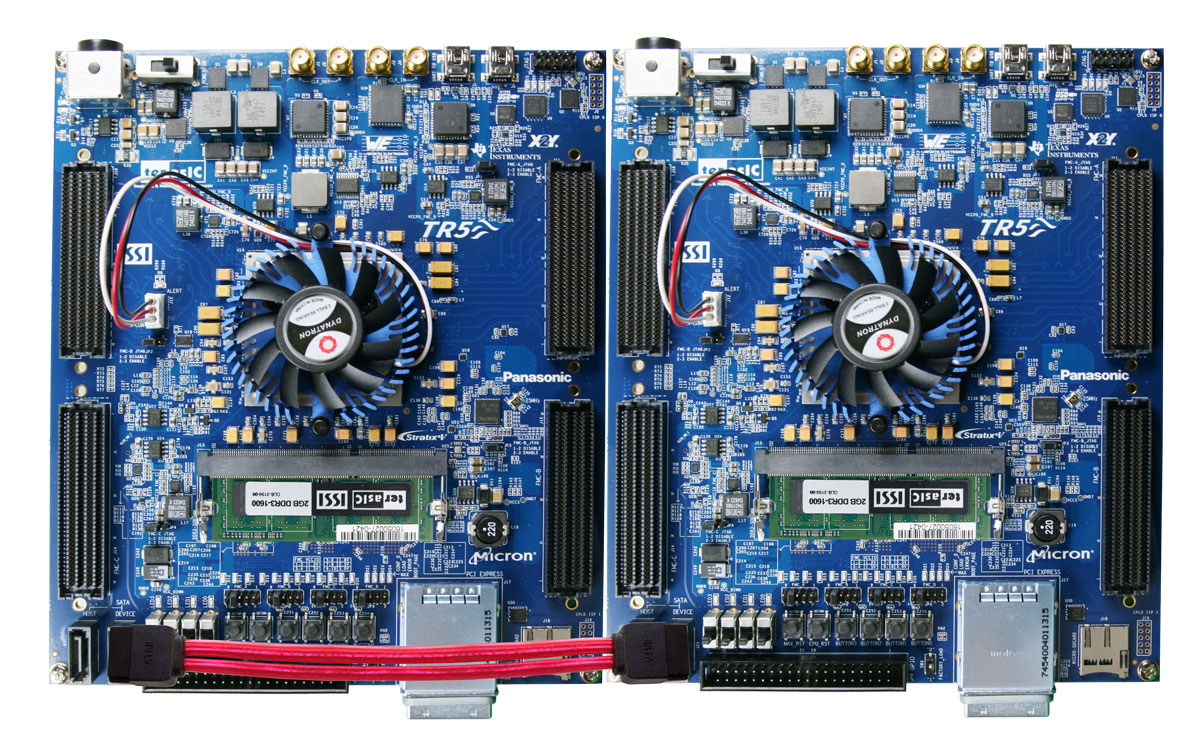

板跟板连接透过 PCIe 连接线

透过 SATA 介面扩充

板跟板连接透过 SATA 连接线

透过 GPIO 介面扩充

连接 D5M

子卡

连接 MTL2

子卡

连接 LT24 子卡