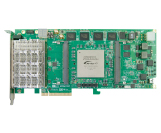

- Altera Stratix® V GX FPGA (5SGXEA7N2F45C2)

- 32MB SRAM (ISSI QUADP for DE5-Net 450, GSI SigmaQuad-II+ for DE5-Net 550, Cypress QDRII+ for DE5-Net 500)

- Up to 8GB DDR3 800 MHz SO-DIMM SDRAM

- Altera Arria 10 GX FPGA (10AX115N2F45E1SG)

- 4個 QSFP+ 連介面和1個 PCI Express (PCIe) x8 連接器

- 2 個獨立 DDR3 SODIMM 插槽和4個獨立 550MHz QDRII+ SRAMs 模塊

- Altera Arria 10 GX FPGA (10AX115N2F45E1SG)

- Four QSFP+ connectors and one PCI Express (PCIe) x8 edge connector

- Two independent DDR4 SODIMM socket and four independent 550MHz QDRII+ SRAMs

由 Altera 和友晶科技連續舉辦 11 年的「亞洲創新設計大賽」,不僅是亞太區最頂尖的 FPGA 設計競賽,更是理工學生視為最高榮譽的競技場。今年總獎項高達美金十萬元,參加大賽的隊伍將有機會獲得首獎獎金 $1,000 美元,以及價值高達 $8,000 美元,搭載 Altera 最新 Stratix V FPGA 的 DE5-Net 開發板 ,作品的技術文稿也將刊登於「亞太FPGA應用工程期刊」及全球線上資料庫,創造全球曝光的機會!

由 Altera 和友晶科技連續舉辦 10 年的『亞洲創新設計大賽』,不僅是亞太區最頂尖的 FPGA 設計競賽,更是理工學生視為最高榮譽的競技場。今年『亞洲創新設計大賽』將與『亞太 FPGA 應用工程期刊』的徵稿競賽合併舉辦,總獎項高達新臺幣五百萬元,即日起至 5 月 24 日止開放線上報名。參加大賽的隊伍將有機會獲得首獎獎金 $1,000 美元,以及價值高達 $8,000 美元,搭載 Altera 最新 Stratix V FPGA 的 DE5-Net 開發板,同時作品的技術文稿也有機會再獲得期刊獎項,邀請各大專院校理工系所的教授與學生一同來展現創意,實現夢想。

友晶在此很高興向各位正式宣布,

DE5-Net

高階開發板已獲得

Altera

官方認證,可在此

FPGA 板

上實現

OpenCL

規範的設計!

為滿足客戶對高速訊號傳輸、先進記憶體介面以及高邏輯單元容量的渴望,友晶科技不斷朝著高頻寬應用面突破,深入了解高頻電子交易、資料擷取和網路與訊號處理等領域,設計出一系列的 28 奈米 Stratix V FPGA 開發平台。此系列包含三種平台:TR5-Lite 輕薄短小不占空間。DE5-NET 可提供最多的記憶體容量、頻寬與最快的速度。TR5-F40W 設計上則是保留最大的彈性,提供規格擴充的便利性。

Terasic DE5-Net board now officially supports the OpenCL Computing Language (OpenCL tm) programming model. Experience the incredible performance boost using our most powerful solution!

麻州大學愛姆赫斯特分校(University of Massachusetts Amherst)近日宣布已經成功將 NetFPGA 計畫實踐在 DE5-Net Stratix V FPGA 高階開發平台上。

Altera為了讓使用者充分運用FPGA之靈活性,並且幫助實現在各種應用上的客製化硬體架構,提供了參考平台的資源;此參考平台同時包含了硬體層及軟體層的設計參考。

Terasic DE5-Net board and DE1-SoC board now officially support the OpenCL Computing Language (OpenCL tm) programming model. Experience the incredible performance boost using our most powerful solution!