在進入 Full HD 的高清影像階段 ( 影像分辨率達到 1920 x 1080 ) ,HDMI 更是 HDTV 不可或缺的一項接口。以 720p 的 HDTV 內容傳輸來說,需要 1.485 Gb/s 的傳輸率才能支持未經壓縮的影音內容,通過 HDMI,就能以每秒 165 Mpixels 的速度傳輸高達 24 位的影音內容,所提供的頻寬可以高達 4 Gb/s,不僅滿足 1080p Full-HD,還能支持以 192kHz 取樣頻率傳輸高達 8 軌的 24 位音訊。 HDMI 1.3 版,其傳輸率從原先的 4.96Gb/s 倍增到 10.2Gb/s,將色深支持從 24-bit 提升到 30bit、36bit 以及 48bit ( RGB 或 YCbCr ),具有輸出一億色以上的能力。剛通過 HDMI1.4a 標準,建築在 HDMI1.4 的基礎上,專門為 3D 立體影像傳輸進行升級和改進。

在 HDTV 及 HDMI 的標準浪潮不斷推波助欄下,許多過去視為單純的分割畫面技術,在 FullHD 的高清畫質條件之下,便成了在硬體上開發的挑戰。為了讓分割後的畫質達到 Full HD 的水平,視訊處理核心的設計方法便成了關注焦點。尤其本文介紹以 DE3 FPGA 平台實現 HDMI Full-HD 1080p 分割畫面處理核心之設計方法。

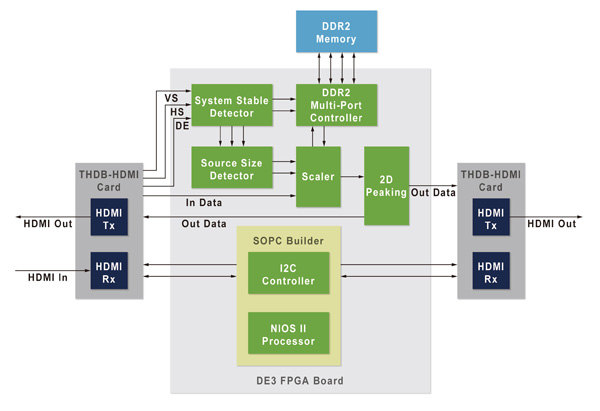

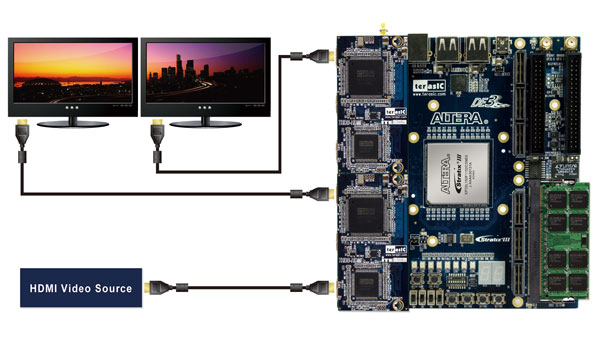

圖1即為基本 HDMI Full-HD 1080p 分割畫面處理器之設計方塊與架構圖。本系統接收一路 HDMI Full-HD 的影像輸入,經過 FPGA 處理後,根據 LCD 螢幕之組合,進行水平及垂直縮放處理,輸出至兩個 (或四個) 1920 x 1080 分辨率的 LCD。圖2為實際以 DE3 FPGA 開發平台加上符合 HDMI 1.3 規範之輸出入子卡所搭建之硬體配置圖。

圖1 < HDMI Full-HD 1080p 分割畫面處理晶片方塊與系統架構圖 >

圖2 < 以 DE3 FPGA 開發平台加上符合 HDMI 1.3 規範之輸出入子卡所搭建的硬體配置圖 >

此系統由三部份組成:

(1) HDMI 輸出入協議設定控制核心;

(2) HDMI 控制信號產生器;

(3) HDMI 影像數據流處理核心。

第一部分 HDMI 輸出入協議設定控制核心,是圖1中 SOPCBuilder 所建立的部份,這個部份是由 NIOS 處理器( NIOS Processor )和 I2C 控制器( I2C Controller )組成,負責正確設定和控制 HDMI 輸出入。第二部分 HDMI 控制信號產生器,是由圖1中系統穩定偵測器( System Stable Detector ),源分辨率計數器( Source Size Detector ) 和 DDR2 多端口控制器( DDR2 Multi-Port Controller )所組成。系統穩定偵測器負責自動偵測不同解晰度影像源的切換,使整個系統有相對應重新設置。源分辨率計數器負責根據前端影像源和後端顯示的分辨率,設定適當的縮放參數,邊框大小和顯示位置。

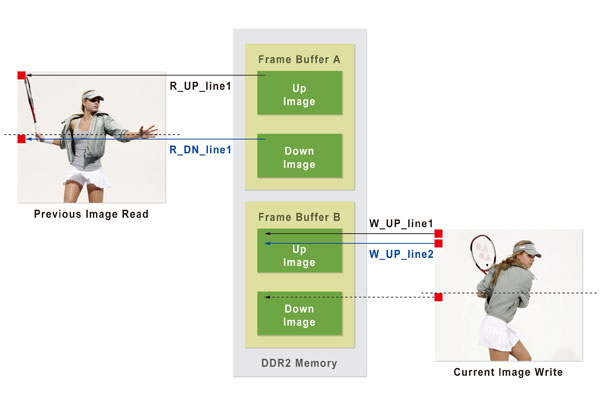

DDR2 多端口控制器負責垂直分割的內存器存取控制,DDR2 內存器要規劃成 Ping-Pong Buffer 的結構( 圖3所示為垂直方向一分為二的例子 ),利用兩個相同的幀儲存器,一幀用來寫,另一幀用來讀,可避免畫面閃爍 ( flick ) 和不連續 ( tearing ) 的副作用。若垂直方向是一分為二,DDR2 多端口控制器,必須規劃成一寫二讀,在寫入的時候也要規劃兩個起始位置,一個寫入上半影像,另一個寫入下半影像,簡化讀取端 DDR2 控制電路的架構。在此設計上各讀取的時間點若有均勻的分配,以圖3為例,分配一行只有一個讀取,即當寫入第一行時,在讀取端只有上面影像第一行的信息會被讀出,而當寫入第二行時,在讀取端也只有下面影像第一行的信息會被讀出。

依此類推,讓 DDR2 的頻寬得到最佳的分配,即使是 148.5 MHz 的 Full-HD 輸入影像源,DDR2 的操作頻率也可以在 200 MHz 以下輕易達成,這樣使得在垂直方向並沒有分割數目的限制。

第三部分 HDMI 影像數據流處理核心是由縮放器( Scaler )和二維峰化器( 2D-Peaking )所組成。縮放器負責將輸影源依照預定輸出分割畫面的大小,做線性或非線性的放大。做插點動作時,參考點數越多,所得到的畫質越佳,建議至少需使用 Bi-Cubic 的插點技術。這邊若能再考慮 Edge-Adaptive,在高頻部份的畫面越能清晰呈現。二維峰化器負責增強影像的銳利度,改善經過縮放後,變模糊的邊界。在此須注意的是若前端縮放器沒有處理好,經過二維峰化器之後,會放大縮放器所產生的副作用如光環 ( Halos ) 和鋸齒狀 ( Jaggies ) 的現象。

實驗平台的搭建如圖2所示,DE3 FPGA 為主平台,負責實現除 HDMI 收發器外的所有功能,實際輸入源由 Sony PS3 具 HDMI 輸出的遊戲機擔任,產生 1920 x 1080 Full HD 1080p 之影像訊號,經 FPGA 將原始之影像訊號分割,分別輸出至兩部 HDMI 螢幕,DE3 平台 上使用之 FPGA 為 Altera Stratix III 340 器件,具 34 萬邏輯單元 ( Logic Element ),實驗結果顯示本系統可在主頻 148.5MHz,內存 DDR II 以 200MHz 執行速度下完成所有任務。

圖3 < DE3 平台之 DDR2 內存器規劃成 Ping-Pong Buffer 的結構– 以垂直方向一分為二為例 >

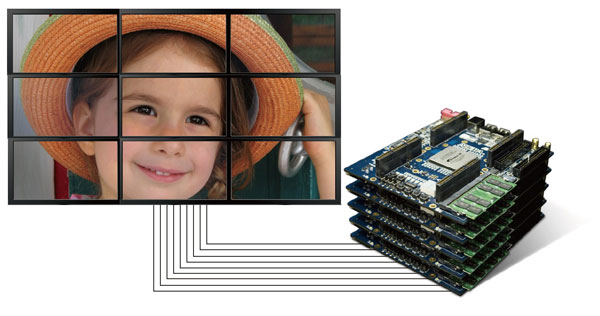

以上述設計方法,可輕易由複製而設計出任意規格 (如 2x2、2x3、3x3、3x4 ) 等 Full-HD 之分割畫面處理晶片。藉由 DE3 平台 的重組及堆棧特性,可任意搭建出所需之硬體開發平台。圖4描述我們在實驗室中以多片 DE3 及 HDMI 子卡搭建平台開發出之 3 x 3 Full-HD HDMI 分割畫面處理器。可用於各類電視牆之應用。

圖4 < 以多片 DE3 平台及子板以堆棧方式設計一進九出之電視牆控制晶片及其開發平台高清影像 >

本文詳細介紹瞭如何設計 HDMI Full-HD 1080p 分割畫面處理核心的技巧,並了解如何使用 DE3 FPGA 開發平台 搭配友晶科技 THDB-HDMI 子卡,完整實現 HDMI 分割畫面處理器的系統方塊。對此實驗細節有興趣的讀者,請參考hdmi.terasic.com