國立台灣科技大學的資訊工程系副教授,劉一宇老師,因應教育部「智慧聯網技術與應用人才培育計畫

」,主導「適用於 RISC-V 指令集架構及記憶體階層的系統級模擬」課程模組,劉教授親自開發教材、於系上試教、進而舉辦一日種子教師培訓,並邀請友晶於課程中擔任業師,希望將此 RISC-V 應用推廣至國內其他學校。

由友晶設計製造、甫在 2019 年推出的 T-Core FPGA

開發板,即因為其定位為適合初學者入門 RISC-V、價格親民符合學習推廣目的,以及不需要額外添購軟體授權,而獲選為此一課程模組的主要教學硬體。

友晶也在產學合作的基礎上,共同參與了劉老師開發 RISC-V 教材的過程,積極提供資源以及建議,在經過長達一年的合作討論和修正,2020年 8 月 28 日一日種子教師培訓終於在國立台灣科技大學正式登場,吸引了多位國內大學教授報名,並偕同學生參加。

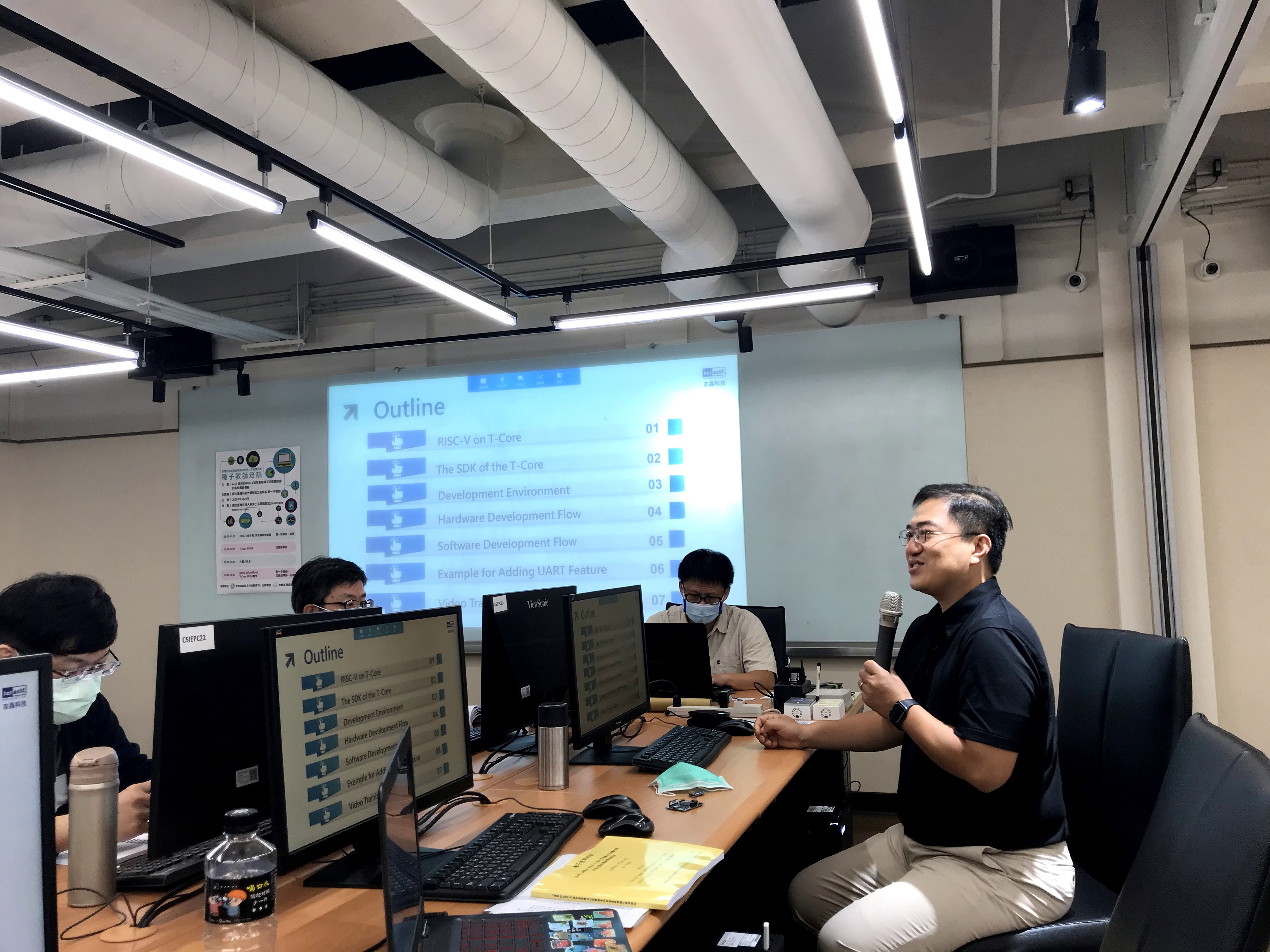

上半場培訓,除了劉教授擔任主講,助教們從旁協助,友晶資深技術經理也以業師身分,到場和所有與會教授、學生們講解 T-Core 架構和如何在開發板上應用 RISC-V。下半場則是讓所有與會成員動手實作,期間大家反應十分熱烈,提問更是踴躍,結訓後仍有不少老師留下和友晶人員請益、交流。

此次寶貴經驗,讓友晶和國內大學能夠互相交流學習。劉教授也欣喜表示,樂見校際間、產學間的良好互動,這樣的合作模式,對於台灣的教育可以有正面的助益。友晶也將秉持這樣的精神,繼續貢獻學界,支持校園人才的培育。

此次培訓之完整課程錄影,已公開於 YouTube 播放清單「教育部智慧聯網技術與應用人才培育計畫 ─ RISC-V 處理器架構、模擬軟體與運用」

認識RISC-V

RISC-V 是近年來崛起的一個基於精簡指令集 (RISC) 原則的開源指令集架構 (ISA) ,相較其他現有的指令集往往授權費昂貴、架構繁複又冗長,初始由 UC-Berkeley 開發的 RISC-V 憑藉其免費、開源的特性受到廣泛關注,大至企業、小至個人都可以自由開發與銷售相容 RISC-V 指令集的處理器和軟體,從而建構出一個鼓勵合作共榮的 RISC-V 軟硬體生態系統。RISC-V 更具有極強的擴展性,從物聯網 (IoT) 切入,應用領域涵蓋微控制器到超級電腦,可說是潛力無限。

秉持開源的精神,並致力打造一個 RISC-V 全球生態圈,2015 年 RSIC-V 基金會誕生,至今更已經吸引超過 150 家全球知名企業和學校加入會員,包括 Google、Samsung、Nvidia,還有普林斯頓大學、北京清大等。

在可見的未來 RISC-V 應用將乘勢而起,甚至改變科技產業的面貌,因此讓國內學子及早熟悉此一架構實在刻不容緩。有鑑於此,教育部將RISC-V 也納入了其「智慧聯網技術與應用人才培育計畫

」的一環,期望從大學紮根,幫助老師、學生儘早和跨領域的應用基礎技術接軌。

劉一宇教授攜台科大研究生團隊蒞臨友晶演示試教成果

友晶資深技術經理到場擔任業師

培訓採用實戰演練方式,教師們動手操作每一個步驟

培訓圓滿落幕,所有與會教師、同學、友晶同仁合影