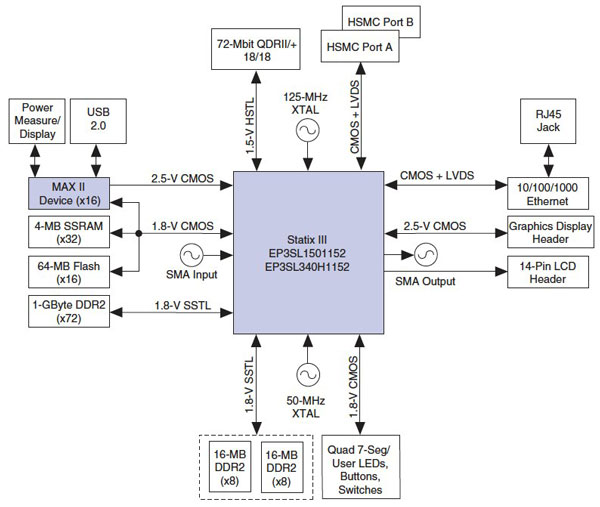

Stratix III EP3SL150F1152 high-performance FPGA

- 142,500 equivalent logic elements (LEs)

- 744 user I/O pins

- 384 18x18 multipliers

Clocking

- 125-MHz oscillator

- 50-MHz oscillator

- SMA input

- SMA output

Configuration

- MAX®

II flash passive serial configuration circuit

- MAX II EPM2210GF256C3N CPLD

- 2,210 LEs

- 272 user I/O pins

- 8-KB user flash memory

- MAX II EPM2210GF256C3N CPLD

- On-board USB-BlasterTM download cable using Quartus® II development software programming

- JTAG download port

General user input and output

- Power consumption display

- Displays each power rail individually

- System reset push button

- Board-specific dual in-line package (DIP) switch

- JTAG bypass DIP switch

- User reset push button

- User push buttons (x4)

- User DIP switch (x8)

- User LEDs (x8)

- User quad 7-segment display

- 128x64 dot pixels graphics display

- LCD (16 character x 2 line)

Memory devices

- 128-MB DDR2 SDRAM DIMM

- 16-MB DDR2 SDRAM devices (individually addressable)

- 36-Mb QDR II SRAM device

- 4-MB PSRAM

- 64-MB flash memory

Components and interfaces

- USB 2.0

- 10/100/1000 Ethernet

- Two HSMC interfaces

Power supplies

- 12-A DC/DC µModule - LTM4601EV

- 1.5-A low-input voltage VLDO linear regulator - LTC3026EDD

- 100-mA, low-noise, LDO micropower regulators in SOT-23 - LT1761ES5-SD

- 4.5-A, 500-kHz step-down switching regulator - LT1374CFE

- 1.2-MHz/2.2-MHz inverting DC/DC converters in ThinSOT - LT1931AES5

- 1-/2-channel 24-bit µPower no latency delta-sigma ADC in MSOP-10 - LTC2402CMS

Altera Stratix III Development Board Block Diagram