现今全球在 10Gb/s 速度以上之高端多层 PCB 设计案例,由于涉及许多高速电路分析理论及仿真技术经验,因而大都还是由欧美大厂主导设计。多数亚洲公司尚未有完整实力能与欧美竞争对手在此利基型市场上相抗衡。随着 FPGA 在制程上不断借 TSMC 与 UMC 等晶圆大厂之力突破,从 90 奈米一路快速发展至 28nm,IO 接口速度从 10Gb/s 不断拉升至近 30Gb/s 的高速,市场对于如何将 FPGA 所需之硬件电路及 PCB 设计一次精确到位的要求, 也急速增加。

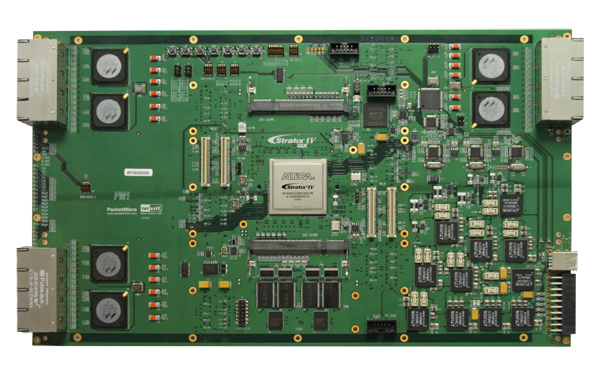

图一 友晶科技为美国航天产业开发之 40 奈米 Stratix IV FPGA 高阶系统

自 2005 年起 Altera 最新 FPGA 系统设计及所有生产转移至友晶科技。 2009 年中,友晶科技为美国航天产业一领导公司开发了 40 奈米 Stratix IV FPGA 高阶系统及所需之高速 PCB 仿真。目前,此系统已顺利通过所有功能测试。图一为此一系统外观,PCB 为 22 层板, 长宽尺寸为 38.2 cm x 23.3 cm。此平台为尖端航天科技在研发及应用上带来新的解决方案。本文将描述在此项目开发过程,所遇到的 PCB 设计难题。

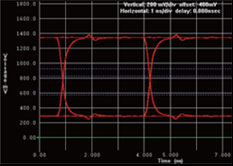

图二 DDR3 Memory 之仿真結果

在高速 40 奈米以下的 FPGA 系统设计过程中,研发人员需要克服不少挑战,并运用包含 SPICE 在内的多种仿真工具,解决高速讯号电路面临的讯号完整性 ( Signal Integrity ) 问题。通过对具体问题进行分析来优化零配件选择和设计折衷,如层迭结构、介电材料、讯号线拓朴结构、线长、线宽和阻抗匹配组件等,并根据仿真结果对设计进行调整,以便在设计阶段解决大多数的讯号完整性问题。 图二为我们使用仿真分析阻抗匹配组件对 DDR3 地址讯号的影响,透过仿真可以看到终端匹配电阻的使用将使讯号拥有较少的 overshoot 与 undershoot 。

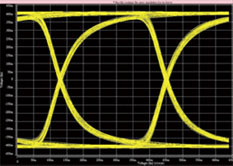

图三 SPICE 眼图结果

为达成 10Gb/s 以上之接头传输,基板层中的介电材料产生的传输损耗现象必需被考虑,因此我们透过 SPICE 仿真来验证板材对损耗的影响。图三为对 10 inch 的传输距离,传输 10Gb/s 时之仿真眼图 ( Eye Diagram ) 。我们发现,在 10Gb/s 的速度下,除了选择低损失正切 ( Loss tangent ) 的材质以减少介电质损耗外,控制损耗的另一个方式是避免跨越转换区域时阻抗的不连续,如过孔和 SMT 器件的焊垫。

过孔损耗

每个过孔独特的特性,包括其衬垫的大小和形状、过孔长度(通孔或盲埋孔)、过孔中不作讯号传输的部分 ( Stub ) 、以及连接导线所在的层数等,都会影响损耗。

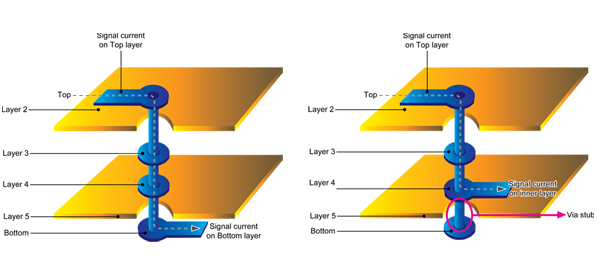

降低过孔所造成的损耗包括在内层不使用衬垫 ( pad ) 并使用较大的抵抗衬垫 ( Anti-pad ) 以降低寄生电容效应;传输线布线在外层 ( top/bottom layer ) ,否则使用盲埋孔或背面钻孔 ( backdrill ) 减少不作讯号传输的部分 ( Stub ) 以降低讯号反射;增加 GND return via 以保持传输线过孔换层走线时,其回流路径能够连续。图四为讯号从 Top layer 至 Inner layer 的过孔换层时所造成的 Via Stub Effect。

图四 Via Stub Effect

SMT 器件焊垫的损耗

FPGA Multi-Gigabit 收发器设计中最常见的组件就是 DC blocking 电容、高速接头和 PCI Express 边缘连接器,当差分讯号走线进入以上这些组件的 SMT 焊垫时,由于 SMT 焊垫的铜箔宽度会较差分讯号走线宽度大,线宽的差异造成阻抗的不同,较窄的走线宽度其阻抗值较高,而较宽的 SMT 焊垫其阻抗值较低。为了使阻抗匹配,我们必需想其它办法来提高经过 SMT 焊垫时的阻抗,使其与走线阻抗相同。

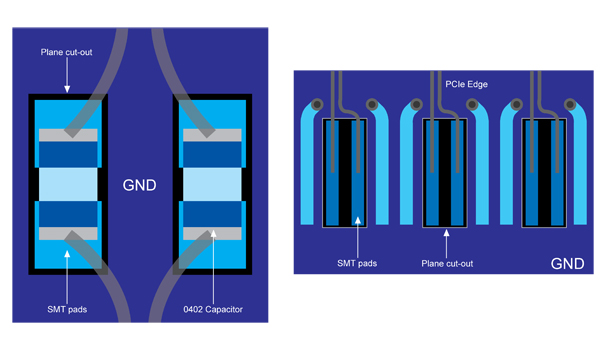

影响阻抗的因素,除了线宽外还有走线层与大铜面参考层的距离、介电层介电常数和走线层铜箔厚度。一旦 PCB 迭构决定后,我们只有改变走线层与大铜面参考层的距离。我们会想办法让走线层参考到第二近的大铜面层,彷佛增加了走线层与大铜面层的介电层厚度而使得阻抗上升,因此我们可以将在 SMT 焊垫下的第一层大铜面挖掉来增加其阻抗,最后达到与走线的阻抗相匹配。图五为我们实际 Layout 上的做法。

图五 改变 Layout 及其阻抗之实际作法

以上多种 PCB 结构都能帮助实现高速串行数据传输,要正确地实现他们可透过模型的建立与仿真分析来掌控损耗对讯号完整性的影响。透过此种设计方法,我们成功将此复杂系统及 PCB 设计一次到位。免除过去 PCB 需要多次修改方能满足特性之窘境 。