現今全球在 10Gb/s 速度以上之高端多層 PCB 設計案例,由於涉及許多高速電路分析理論及仿真技術經驗,因而大都還是由歐美大廠主導設計。多數亞洲公司尚未有完整實力能與歐美競爭對手在此利基型市場上相抗衡。隨著 FPGA 在製程上不斷借 TSMC 與 UMC 等晶圓大廠之力突破,從 90 奈米一路快速發展至 28nm,IO 接口速度從 10Gb/s 不斷拉升至近 30Gb/s 的高速,市場對於如何將 FPGA 所需之硬體電路及 PCB 設計一次精確到位的要求,也急速增加。

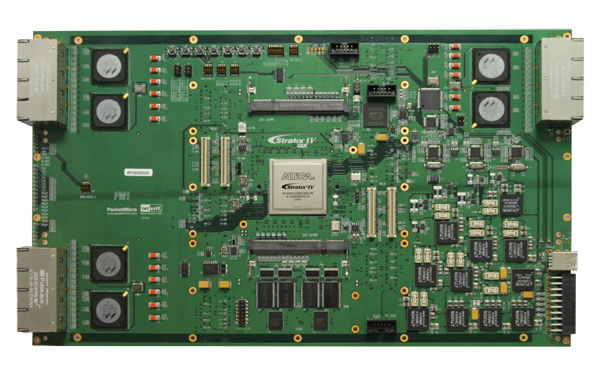

圖一 友晶科技為美國航空產業開發之 40 奈米 Stratix IV FPGA 高階系統

自 2005 年起 Altera 最新 FPGA 系統設計及所有生產轉移至友晶科技。 2009 年中,友晶科技為美國航天產業一領導公司開發了40 奈米 Stratix IV FPGA 高階系統及所需之高速 PCB 仿真。目前,此系統已順利通過所有功能測試。圖一為此一系統外觀,PCB 為22 層板,長寬尺寸為 38.2 cm x 23.3 cm。此平台為尖端航天科技在研發及應用上帶來新的解決方案。本文將描述在此項目開發過程,所遇到的 PCB 設計難題。

圖二 DDR3 Memory 之仿真結果

圖三 SPICE 眼圖結果

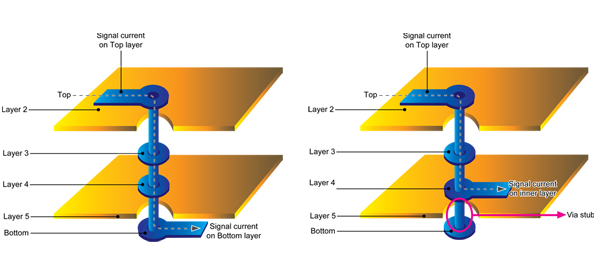

過孔損耗

每個過孔獨特的特性,包括其襯墊的大小和形狀、過孔長度(通孔或盲埋孔)、過孔中不作訊號傳輸的部分 (Stub) 、以及連接導線所在的層數等,都會影響損耗。

降低過孔所造成的損耗包括在內層不使用襯墊 (pad) 並使用較大的抵抗襯墊 (Anti-pad) 以降低寄生電容效應;傳輸線佈線在外層 ( top/bottom layer ) ,否則使用盲埋孔或背面鑽孔 ( backdrill ) 減少不作訊號傳輸的部分 ( Stub ) 以降低訊號反射;增加 GND return via 以保持傳輸線過孔換層走線時,其回流路徑能夠連續。圖四為訊號從 Top layer 至 Inner layer 的過孔換層時所造成的 Via Stub Effect。

圖四 Via Stub Effect

SMT 器件焊墊的損耗

FPGA Multi-Gigabit 收發器設計中最常見的組件就是 DC blocking 電容、高速接頭和 PCI Express 邊緣連接器,當差分訊號走線進入以上這些組件的 SMT 焊墊時,由於 SMT 焊墊的銅箔寬度會較差分訊號走線寬度大,線寬的差異造成阻抗的不同,較窄的走線寬度其阻抗值較高,而較寬的 SMT 焊墊其阻抗值較低。為了使阻抗匹配,我們必須想其它辦法來提高經過 SMT 焊墊時的阻抗,使其與走線阻抗相同。

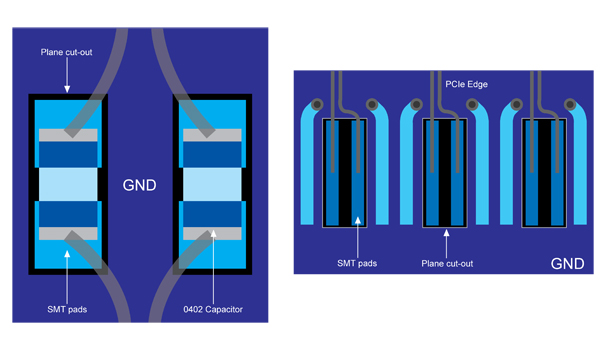

影響阻抗的因素,除了線寬外還有走線層與大銅面參考層的距離、介電層介電常數和走線層銅箔厚度。一旦 PCB 疊構決定後,我們只有改變走線層與大銅面參考層的距離。我們會想辦法讓走線層參考到第二近的大銅面層,彷彿增加了走線層與大銅面層的介電層厚度而使得阻抗上升,因此我們可以將在 SMT 焊墊下的第一層大銅面挖掉來增加其阻抗,最後達到與走線的阻抗相匹配。圖五為我們實際 Layout 上的做法。

圖五 改變 Layout 及其阻抗之實際作法

以上多種 PCB 結構都能幫助實現高速串行數據傳輸,要正確地實現他們可透過模型的建立與仿真分析來掌控損耗對訊號完整性的影響。透過此種設計方法,我們成功將此複雜系統及 PCB 設計一次到位。免除過去 PCB 需要多次修改方能滿足特性之窘境。