课程名称

RISC CPU 架构设计及SOPC系统实作 (工业局半导体学院IC设计类短期课程)

下载课程简章

课程目标

- 详细介绍 RISC CPU 之架构

- Pipeline 指令集之设计,

- 外围IP整合, 客制指令, 及 DMA 概念

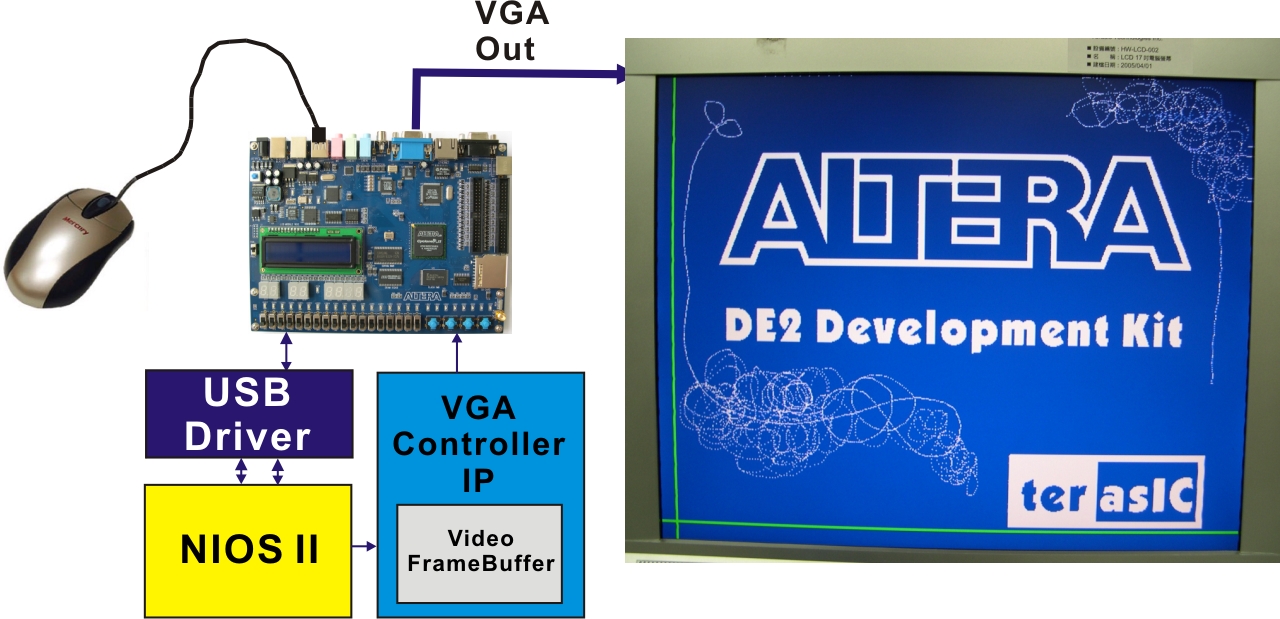

- 以 Altera Nios II CPU及其 SOPC系统为实作范利做完整的说明.

- 本课程将详细介绍 Nios II CPU及其系统架构,并针对系统整合所需要的User Peripheral、Custom Instruction、DMA与Driver开发,做完整的说明。

- 本课程将在Altera DE2开发板上设计及实作SOPC 整合开发.

- 以一人一机方式让学员实作专题 - 网络封包收发及SD 卡音乐拨放器等。使学员可以在最短的时间内,以SOPC系统整合,并且在Nios II CPU上完成系统开发

课程大纲

- RISC CPU 架构

- Pipeline 原理图解

- Instruction Set 设计

- Register File 组织

- Nios II CPU Architecture.

- SOPC Design Flow.

- Avalon Switch Fabric and Bus Protocol.

- Adding a User Peripheral.

- Custom Instruction.

- Multi-Masters and Direct Memory Access.

- Altera 开发板功能介绍(每个学员一片, 以独立制作专题)

- SOPC专题实作1 : (以NIOSII CPU 实作以太网络封包收送)

- SOPC专题实作2 : (以NIOSII CPU 实作SD卡音乐拨放器)

报名资格及费用

报名资格需为在职业界人士,并有相关工作背景,学员自费 NTD$5,400 ,工业局补助 $5,000 。

授课日期及时数

- 假日班: 2006/10/14~2006/10/28 每週六 10:00-17:00

- 每班仅招收 30 位学员,授课总时数为 18 小时

上课地点

友晶科技新竹总公司训练教室

教材下载

- 请参考友晶科技为Altera ODM 之 DE2 全球多媒体开发平台网页 (进入DE-2选项中有非常详细的介绍与光盘/实验下载)

课程报名表