在进入 Full HD 的高清影像阶段 ( 影像分辨率达到1920 x 1080 ),HDMI 更是 HDTV 不可或缺的一项接口。以 720p 的 HDTV 内容传输来说,需要 1.485 Gb/s 的传输率才能支持未经压缩的影音内容,通过 HDMI,就能以每秒 165 Mpixels的速度传输高达 24 位的影音内容,所提供的频宽可以高达 4 Gb/s,不仅满足 1080p Full-HD,还能支持以 192kHz 取样频率传输高达 8 轨的 24 位音讯。 HDMI 1.3版,其传输率从原先的 4.96Gb/s 倍增到 10.2Gb/s ,将色深支持从 24-bit 提升到 30bit 、 36bit 以及 48bit ( RGB或YCbCr ),具有输出一亿色以上的能力。刚通过 HDMI1.4a 标准,建筑在 HDMI1.4 的基础上,专门为 3D 立体影像传输进行升级和改进。

在 HDTV 及 HDMI 的标准浪潮不断推波助栏下,许多过去视为单纯的分割画面技术,在 FullHD 的高清画质条件之下,便成了在硬件上开发的挑战。为了让分割后的画质达到 Full HD 的水平,视讯处理核心的设计方法便成了关注焦点。 尤其本文介绍以 DE3 FPGA 平台 实现 HDMI Full-HD 1080p 分割画面处理核心之设计方法。

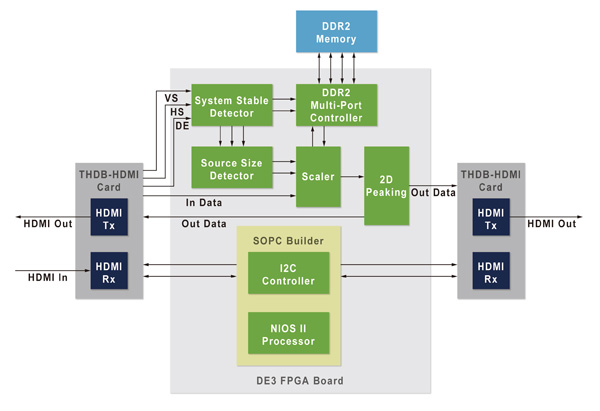

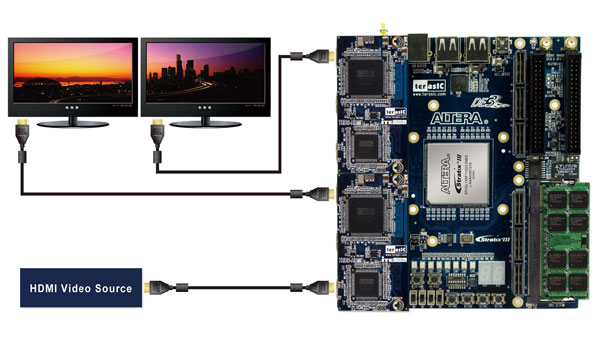

图1即为基本 HDMI Full-HD 1080p 分割画面处理器之设计方块与架构图。本系统接收一路 HDMI Full-HD 的影像输入,经过 FPGA 处理后,根据 LCD 屏幕之组合,进行水平及垂直缩放处理,输出至两个 ( 或四个 ) 1920 x 1080 分辨率的 LCD。图2为实际以 DE3 FPGA 硬件平台 加上符合 HDMI 1.3 规范之输出入子卡所搭建之硬件配置图。

图1 < HDMI Full-HD 1080p 分割画面处理芯片方块与系统架构图>

图2 <以 DE3 FPGA 硬件平台加上符合 HDMI 1.3 规范之输出入子卡所搭建的硬件配置图>

此系统由三部份组成:

(1) HDMI 输出入协议设定控制核心;

(2) HDMI 控制信号产生器;

(3) HDMI 影像数据流处理核心。

第一部分 HDMI 输出入协议设定控制核心,是图1中 SOPCBuilder 所建立的部份,这个部份是由 NIOS 处理器 ( NIOS Processor )和I2C控制器( I2C Controller )组成,负责正确设定和控制 HDMI 输出入。第二部分 HDMI 控制信号产生器,是由图1中系统稳定侦测器( System Stable Detector ),源分辨率计数器( Source Size Detector )和 DDR2 多端口控制器( DDR2 Multi-Port Controller )所组成。系统稳定侦测器负责自动侦测不同解晰度影像源的切换,使整个系统有相对应重新设置。源分辨率计数器负责根据前端影像源和后端显示的分辨率,设定适当的缩放参数,边框大小和显示位置。

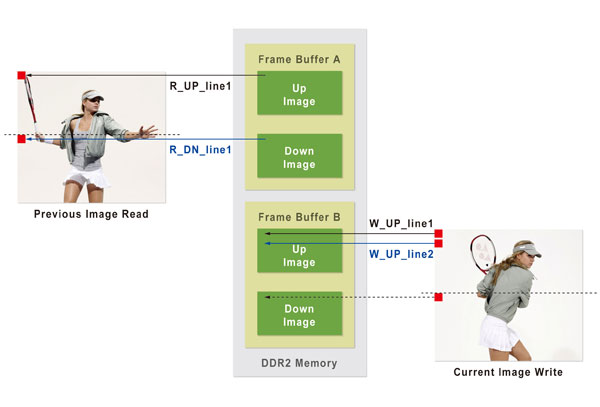

DDR2 多端口控制器负责垂直分割的内存器存取控制,DDR2 内存器要规划成 Ping-Pong Buffer 的结构( 图3所示为垂直方向一分为二的例子 ),利用两个相同的帧储存器,一帧用来写,另一帧用来读,可避免画面闪烁 ( flick ) 和不连续 ( tearing ) 的副作用。若垂直方向是一分为二,DDR2 多端口控制器,必须规划成一写二读,在写入的时候也要规划两个起始位置,一个写入上半影像,另一个写入下半影像,简化读取端 DDR2 控制电路的架构。在此设计上各读取的时间点若有均匀的分配,以图3为例,分配一行只有一个读取,即当写入第一行时,在读取端只有上面影像第一行的信息会被读出,而当写入第二行时,在读取端也只有下面影像第一行的信息会被读出。

依此类推,让 DDR2 的频宽得到最佳的分配,即使是 148.5 MHz 的 Full-HD 输入影像源,DDR2 的操作频率也可以在 200 MHz 以下轻易达成,这样使得在垂直方向并没有分割数目的限制。

第三部分 HDMI 影像数据流处理核心是由缩放器( Scaler )和二维峰化器( 2D-Peaking )所组成。缩放器负责将输影源依照预定输出分割画面的大小,做线性或非线性的放大。做插点动作时,参考点数越多,所得到的画质越佳,建议至少需使用 Bi-Cubic 的插点技术。这边若能再考虑 Edge-Adaptive,在高频部份的画面越能清晰呈现。二维峰化器负责增强影像的锐利度,改善经过缩放后,变模糊的边界。在此须注意的是若前端缩放器没有处理好,经过二维峰化器之后,会放大缩放器所产生的副作用如光环 ( Halos )和锯齿状 ( Jaggies ) 的现象。

实验平台的搭建如图2所示,DE3 FPGA 为主平台,负责实现除 HDMI 收发器外的所有功能,实际输入源由 Sony PS3 具 HDMI 输出的游戏机担任,产生 1920 x 1080 Full HD 1080p 之影像讯号,经 FPGA 将原始之影像讯号分割,分别输出至两部 HDMI 屏幕,DE3 平台 上使用之 FPGA 为 Altera Stratix III 340 器件,具 34 万逻辑单元 ( Logic Element ),实验结果显示本系统可在主频 148.5MHz,内存 DDR II 以 200MHz 执行速度下完成所有任务。

图3 < DE3 平台之 DDR2 内存器规划成 Ping-Pong Buffer 的结构 – 以垂直方向一分为二为例 >

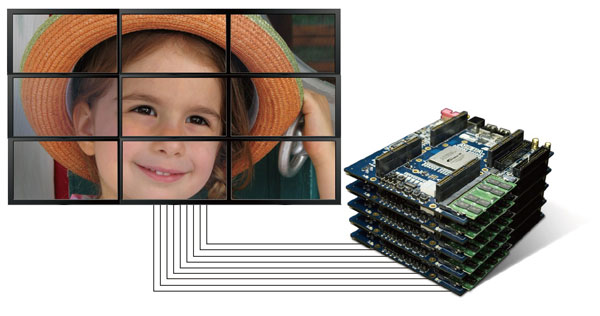

以上述设计方法, 可轻易由复制而设计出任意规格 ( 如 2x2、2x3、3x3、3x4 ) 等 Full-HD 之分割画面处理芯片。藉由 DE3 平台 的重组及堆栈特性,可任意搭建出所需之硬件开发平台。图4描述我们在实验室中以多片 DE3 及 HDMI 子卡搭建平台开发出之 3 x 3 Full-HD HDMI 分割画面处理器。可用于各类电视墙之应用。

图4 < 以多片 DE3 平台及子板以堆栈方式设计一进九出之电视墙控制芯片及其开发平台高清影像 >

本文详细介绍了如何设计 HDMI Full-HD 1080p 分割画面处理核心的技巧,并了解如何使用 DE3 FPGA 开发平台 搭配友晶科技 THDB-HDMI 子卡,完整实现 HDMI 分割画面处理器的系统方块。对此实验细节有兴趣的读者,请参考hdmi.terasic.com