A Review of the Cyclone V GX Starter Kit

Orlando Arias

My name is Dr. Orlando Arias and I am an Assistant Professor of Electrical and Computer Engineering at the University of Massachusetts Lowell. I head the Secure by Design Laboratory at the university which focuses on hardware-assisted cybersecurity solutions, methods for HDL analysis, and fault characterization. I also teach Advanced Digital Systems Design (ADSD), a hybrid graduate and undergraduate class as well a Practical Hardware Security and Cryptography class. It must be said that Intel and Terasic’s unyielding support has made these classes the success they are. We would like to express our gratitude for their help in ensuring that we have both quality software and hardware for students to utilize.

We are starting to utilize the Cyclone V GX Starter Kit in ADSD to great success. We lend these boards to students for the duration of the semester so that they can work outside of class. The boards are of high quality and mechanically sturdy, which allows for ease of transport. The acrylic shield further protects the board from extraneous components falling on top of the delicate components while students are performing experiments.

In class, students make use of the board to create unclonable functions, computational accelerators to generate fractals in real time, perform timing closure on designs that contain multiple clock domains, as well as develop and package intellectual property cores. With the Cyclone V GX Starter Kit, students are able to see the physical manifestation of their hardware designs, bringing a satisfying conclusion to their efforts. The kit is extremely easy to use, is effortless to get started with, and provides a genuinely enjoyable user experience.

We are so satisfied with the kit and its performance that we are currently experimenting with the ability to use this board in other classes, such as Computer Architecture as well as Microprocessors I and II. In collaboration with Jesse Taube, a Junior Undergraduate student, we are developing multiple RISC-V cores for students to experiment with on real devices, not just a simulation environment. We are planning on using the IP developed by students in ADSD in conjunction with these RISC-V cores to further enhance student experience. With this, students will be able to write software for the same cores they have developed, further rounding our Computer Engineering curriculum.

The Cyclone V GX Starter Kits are also being used by students in directed studies-based projects. The collection of on-board peripherals allows for students to perform a wide array of experiments and projects without the need for external hardware. Furthermore, easy integration with already existing hardware by providing Arduino-compatible headers extends the capabilities of an already capable platform to stratospheric heights. Overall, the Cyclone V GX Starter Kits is phenomenal, and it has allowed us to enhance our curriculum to new heights. We would like to once again thank Intel and Terasic for providing us with these materials. We are happy to share images of our success in this front. These can be found below.

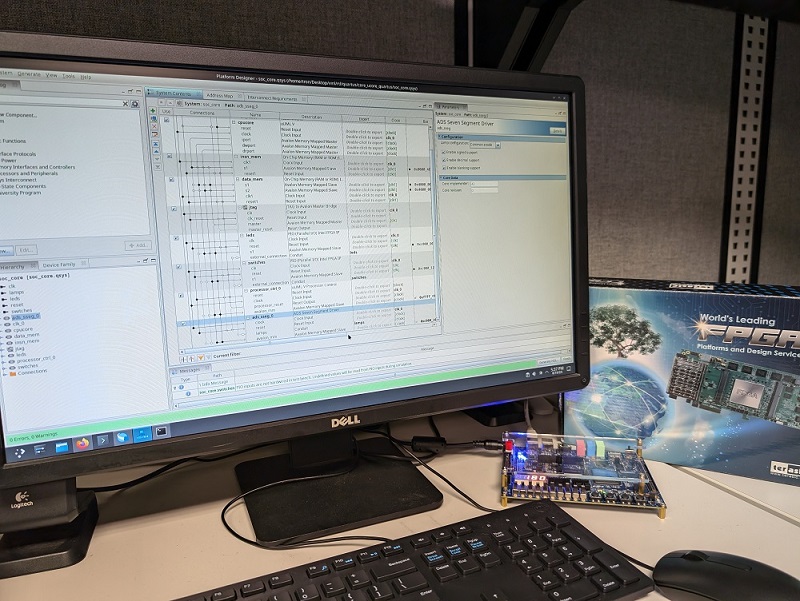

(a) Laboratory computer setup running Quartus Prime and FPGA board connected to machine.

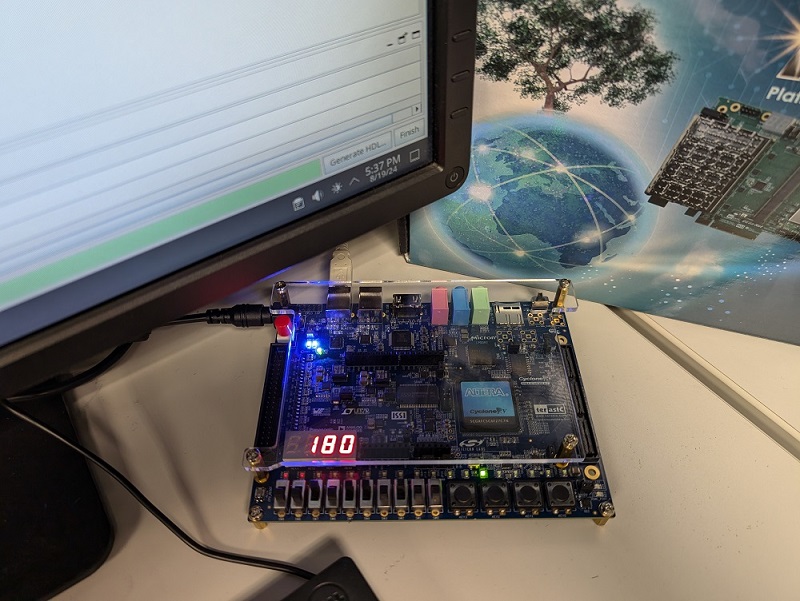

(b) Prototype of the μUML-V (read as micro UML five) core on the FPGA, a core being developed for our Computer Architecture class. The seven segment displays are being driven by an IP core developed in Advanced Digital Systems Design.

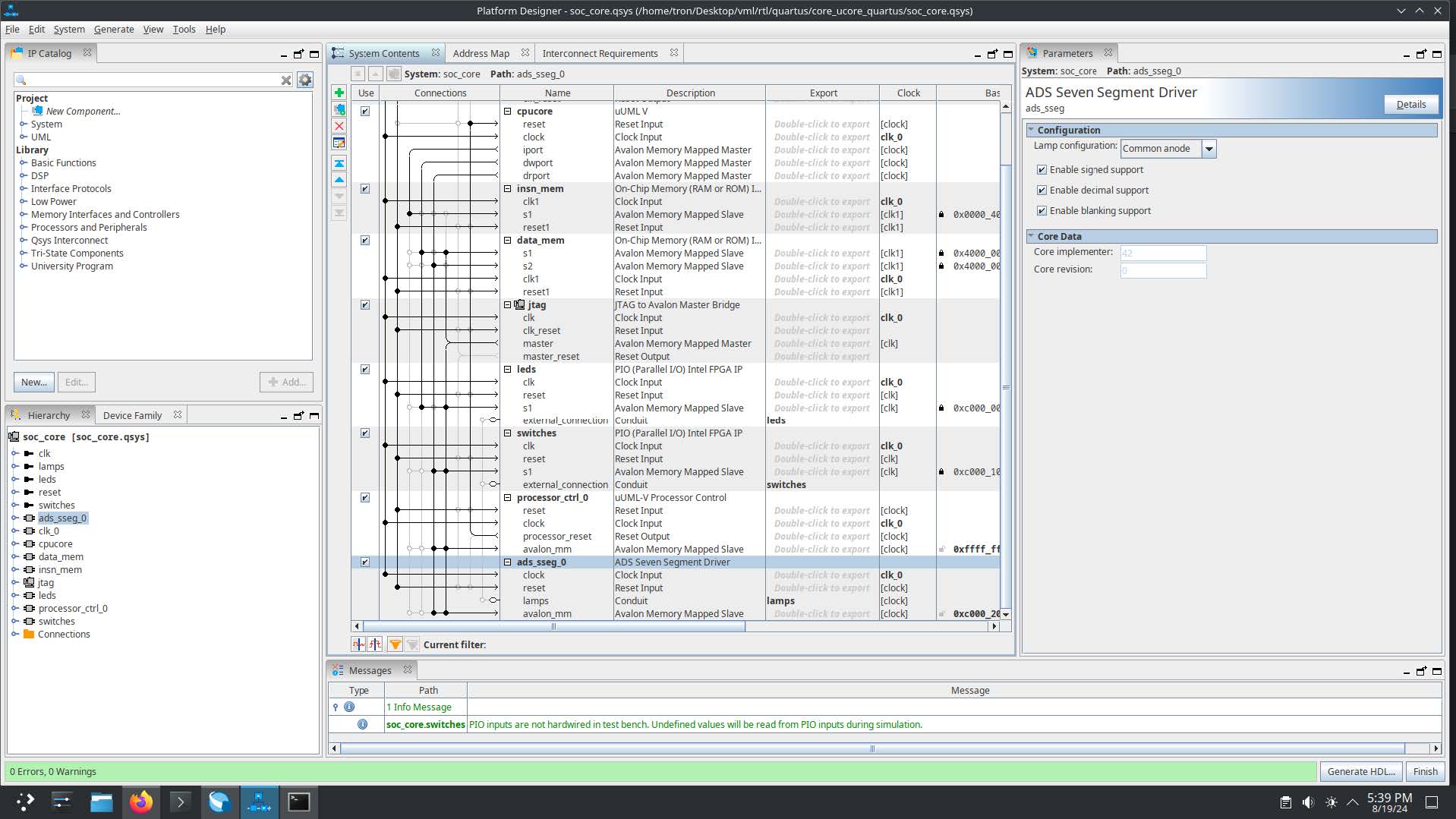

(c) Prototype SoC with the μUML-V core and peripherals.

Professor: Dr. Orlando Arias

University of Massachusetts Lowell

The University of Southern Mindanao, Department of Electronics Engineering, extends its heartfelt gratitude to Intel® and Terasic for the generous donation of FPGA boards. These advanced tools are enabling our students to gain practical experience and enhance their learning in digital design and system implementation.

|

About e-Yantra

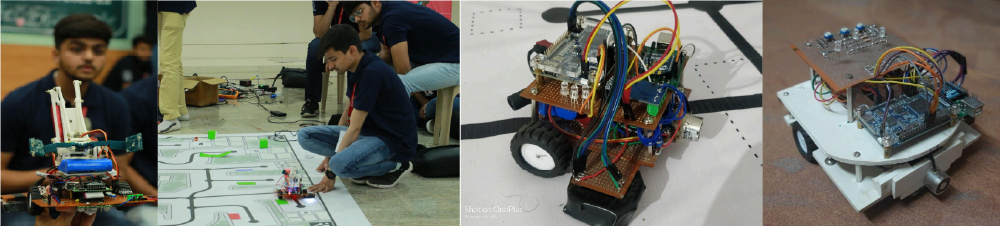

e-Yantra – a project in the Department of Computer Science and Engineering (CSE), IIT Bombay, Mumbai, INDIA - is a flagship project of the Ministry of Education (MoE) through the National Mission on Education through ICT (NMEICT) to spread Embedded systems and Robotics education in colleges across India. e-Yantra complements the existing higher education system through project-based learning. e-Yantra, a robotics outreach project at IIT Bombay has successfully trained over 200,000+ students through various initiatives, and a popular one is the Robotics competition among young engineers in India.

Training and Competition e-Yantra Robotics Competition (eYRC) e-Yantra’s signature robotics competition started in 2012 and this year we have trained 10,800 students through our competition in complex engineering skills through project based learning. Every year we have different problem statements divided into themes.

Since 2020, we have been using DE0-Nano boards to train students in our yearly competition. The problem statement centred around leveraging the DE0-Nano board's capabilities. Our training has covered various topics, including Verilog HDL for FPGA programming, sensor interfacing, actuators and pick-place mechanism, harnessing parallel processing for enhanced computational efficiency, developing sophisticated path planning algorithms, and integrating wireless communication. A pinnacle of our training evolution this year was the implementation of a RISC-V CPU on theFPGA. This significant thematic shift challenged our team and highlighted the DE0-Nano board's adaptability and performance in handling complex computational tasks. Some of the features of the DE0-Nano board we found helpful over other products:

- Form factor: support of the ~22K LUTs with 32MB SDRAM available makes it the right choice for the application we want to develop.

- Easy to use: for beginners, the board comes in handy for porting the design from Quartus software on the FPGA; it is functionally easy to set up the tools and realise the design.

- Support: the documentation

e-Yantra is a flagship project of the Ministry of Education that is conducted by us at IIT Bombay that runs such competitions to train young engineers by challenging them to solve real-world problems through robotics. This year's edition, themed "Space Exploration," features the Astro-Tinker' theme that has the participants learn Verilog programming to program a robot built using your FPGA board.

We wish to invite your team to the e-Yantra Robotics Competition Grand Finale on March 22nd - 23rd, 2024 at IIT Bombay. We'd be happy to have your team member as a Jury member for the AstroTinker Bot (AB) on March 22, 2024 at 1615 to 1800 (IST) where students will showcase their work around the DE0-Nano board.

|

Ajit M Harpude Assistant Project Manager. |

Intel Israel Innovation team

Intel Israel Innovation team has been diving deep into the world of FPGA education and prototyping, specifically using Altera's powerful platforms, and the experience has been nothing short of transformative. Running workshops focused on creating retro games directly on RTL with VGA screens has opened up a new dimension of creativity and learning. The feedback from participants has been overwhelmingly positive, showcasing the engaging and educational nature of these sessions.

We've been utilizing Terasic platforms, which have proven to be exceptionally reliable and versatile for our competitions. Their performance and compatibility with Altera FPGAs have significantly contributed to the success of our workshops, allowing participants to push the boundaries of digital design and gaming.

We highly recommend our workshops to anyone interested in diving into FPGA development or looking to relive the classic era of retro gaming with a modern twist. It's a unique opportunity to learn, create, and compete. We invite everyone to join us on this exciting journey at cpugarage.co.il, where the world of FPGA opens up endless possibilities for innovation and fun.

You are welcome to get a look at our latest competition where engineers and students developed games on RTL alone: https://cpugarage.co.il/competitions/2 .

|

Avi Salmon Head of Intel Israel innovation office. |

Swiss Federal Institute of Technology EPFL

Terasic has been a great partner in providing wonderful FPGA boards. We have been using several models in research over many years. We have also been using the DE10-Lite board in classes related to digital systems design. Students are guided in hands-on laboratory sessions, and then carry over a prototyping project using the on-board modules as well as additional extension boards or modules that are placed on the GPIO extension ports. The boards are very reliable and the development environment is very flexible which creates excellent conditions for an efficient learning curve during the class and also further in self-teaching, as the boards are commercially available at a reasonable price.

|

SProf. Alexandre Schmid Head, EPFL SCI STI AXS Group |

Altera (Now Intel® )

我在 Altera 負責行動回程網路/電信級乙太網路轉換工程;我們使用友晶 SFP-HSMC 子板連接 Altera 開發板來建立乙太網路開關,受用無窮。

Mark Lewis,

Altera (現為 Intel®

)工程經理

AGH University of Science and Technology

我叫 Jacek Dlugopolski。我住在波蘭,在克拉科夫的 AGH 科技大學工作。 我是一個對於所有創新、充滿未來性的技術以及理論有著滿腹熱情的人,而 FPGA 就是這樣的技術之一。

能夠理解 FPGA 技術的優勢和可能性就像發現地球並不是平坦的那樣令人驚奇,而是在三度空間或更三度世界中以各種方式相互影響的眾多其他平行天體之一。

從使用微處理器到使用 FPGA 的演進過程其實有點像從平面世界演進到量子宇宙的過程那樣。FPGA 擁有大規模并行計算的特點,提供了建構並行信息處理演算法的驚人能力,進而避免過多不必要的延遲,更有效地模擬了我們現實世界的行為。

我非常感謝友晶推廣這項技術並創建了許多不同的模塊來幫助人們使用 FPGA。 我個人使用了許多友晶的產品,例如:DE2 ,DE2-70 ,DE0-nano ,DE10-lite 和其他 Intel® 的產品:Cyclone,MAX10 和 Stratix FPGA 系列。所有這些友晶經過專業設計和製造的產品,都非常有幫助,並且非常可靠。

|

School: AGH University of Science and Technology Jacek Dlugopolski Position: Senior Lecturer |

Design Spark

總體而言,DE0-Nano 不僅外觀精巧,同時有著實用的介面,CD-ROM 內容更為豐富,包含電路圖、板卡資訊、以及許多設計工具;此外,CD 中並提供包含詳解步驟的設計範例教你如何建立自己的 FPGA 專案與 NIOS II 處理程序。我認為這片開發板非常適合做為 FPGA 入門者的墊腳石。

Paul Clarke via Design Spark

Russian Space Systems

“我的 FPGA 編程經驗是從我購買 DE0 Nano 開始的。我相信我很幸運買了那塊板,因為 DE0 Nano 通過詳細描述如何創建第一個項目,代碼幫助我完成了 FPGA 編程的第一步。用戶手冊中的第一個程序以及如何對設備進行編程。此板具有開始編程 FPGA 所需的一切:

- 詳細說明用戶手冊;

- 編程器、配置閃存芯片和 FPGA Cyclone IV 在一塊板上;

- 許多引腳來控制您的設計行為並將它們連接到某個地方;

- 低成本。

我喜歡 DE0 Nano ,然後我買了 DE10 Nano 。它具有高性能 SoC:Cyclone V FPGA 和 ARM 處理器。它還可以將 Arduino 板連接到 DE10 Nano 。今天我得到了 Max 10 Plus Board 。我所有的採購都有高質量和非常有吸引力的價格。我希望我會喜歡 Max 10 Plus Board ,就像我喜歡使用 Nano 板一樣!”

|

Galiev Rinat, Electronic Engineer Russian Space Systems |

Hasselt University

"感謝友晶科技﹐你們高質量的產品﹐特別好的服務和熱情幫忙。

使用友晶科技的板子上課很有意思﹐學生的反應很好。謝謝友晶科技同仁們的幫忙和友誼﹗"

"我的課程幾乎都用友晶科技的 DE1-SoC 板子,讓學生可以用 FPGA 板去做實驗和專題。附上這個學期學生用友晶 FPGA 板做的實驗

https://www.youtube.com/watch?v=dduZ2esiUhk "

Prof. Luc CLAESEN,

Professor of Engineering Technology,

Hasselt University, Belgium

Lawrence Berkley National Laboratory

對於彭顯恩先生及魏淑婷小姐帶領的友晶科技研發團隊所提供的無懈可擊服務,我想表達我無盡的感謝。我們一起設計出有著 20 層結構的複雜開發板,同時此片開發板包含了三片 FPGA、DRAM、SRAM、快閃記憶體、乙太網路、USB、RS-232 等許多的原件。從很多層面來看,這塊板子已經是一塊多功處理器電腦系統板,唯一不同之處,在於此塊板子使用的是 FPGA 而非微處理器...more

|

William W. Moses – Senior Staff Scientist, IEEE Fellow, Lawrence Berkley National Laboratory, Califonia |

Lawrence Berkley National Laboratory

友晶所提供的服務,遠超過我們的想像!友晶不僅提供關於本計畫的完整圖式,亦定義了設計錯誤的修正與設計升級的范式,在制造過程中,更要求完善的測試流程。與友晶的繁復討論過程中,友晶盡其可能滿足我們的制作要求,即便須自行吸收增加的成本,依舊能在期限內完成此專案。這不僅是高品質的研發能力,更是高規格的制程表現。這次的成功合作,讓我們建立與友晶的信賴關系,希望未來能有機會繼續與友晶合作。more

|

Woon-Seng Choong – Staff Scientist, new Principle leader for this OpenPET project Lawrence Berkley National Laboratory, Califonia |

McGill University

我從 1997 年開始教中級數位電路設計課程跟實驗。1998 年開始用 Altera 的開發板和 Quartus 軟體。

2008 年後,我們改用友晶的 FPGA 開發板,如 DE1 和近期的 DE1-SoC 。板子和 Altera Quartus 軟體搭配,非常適合在課堂上給學生做練習。學生能夠用 VHDL 設計數字硬件,編譯並下載到 Terasic 開發板,再去測試他的設計還有除錯。新進的 SoC 開發板則提供學生練習軟硬體協同設計的機會,讓我們能更好的銜接上計算機工程學近期課綱的變化。

最後我也要感謝大學計畫,提供大量的教材,幫助我們開發課程、也讓學生得到更多實用的資訊。

Professor James Clark–

Department of Electrical and Computer Engineering, McGill University

Manhattan College

我非常高興能與 Altera 以及友晶接觸,並在最短的時程內訂購並且收到了板卡。我原本希望在來年一月開學時能將一切準備就緒,但板卡十月中就寄到了!這使我有機會能夠更早開始使用新板卡,更好的是,我也有了實物讓我在本學期的數位系統入門課程中使用。

學生們相當熱愛使用新板卡以及附帶軟體,也殷殷期盼在下學期的計算機組織課程中使用。我們希望大學四年的課程裡有更多計算機工程計畫的核心以及選修課堂都能有這樣的硬體環境。現在我們的第一步便是籌措資金更換效能更好的個人電腦以利執行 Quartus 軟體。

Doug Godsoe, Ph.D.

曼哈頓大學 電機工程/計算機工程助教

Milwaukee School of Engineering

我的大學十分仰賴 DE0-Nano SoC 以及 LT24 觸控子板,我們透過這些板子學習數位邏輯和嵌入式系統。以一個學生的角度來說,友晶的產品真的很可靠,又容易上手,並且有豐富的周邊學習資源可以利用。

Hughes Kevin

資訊科學系大四生

密爾瓦基工學院,美國

Multimedia University

我們非常感謝友晶科技設計製造了許多介面豐富的 FPGA 開發板,同時提供學術界非常實惠的價格。這些板子讓我們能夠學習並操作最新的數位邏輯設計技術及嵌入式系統;這些寶貴的經驗絕對能幫助我們成為未來的數位邏輯設計師。非常謝謝你們的努力!

Thum Chia Chieh,

Lecturer, Faculty of Engineering and Technology Multimedia University

North Carolina Agricultural and Technical State University

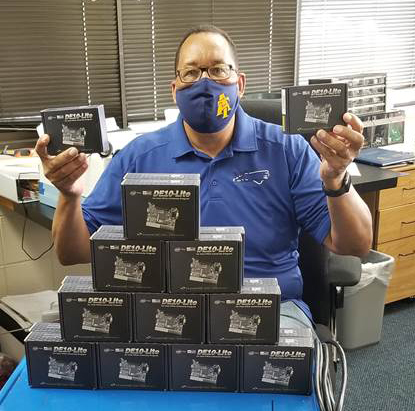

團隊與個人感謝您。我知道你們每個人都為我們如此迅速地獲得了 85 片 MAX 10 DE10-Lite FPGA 板 而創造了“奇蹟”。我們已經將它們分發給我們的學生。更多好消息等著你。

感謝北卡羅來納州農業技術州立大學工程學院的所有人。

Dr. John Kelly

Dr. John Kelly

Associate Professor

North Carolina Agricultural and Technical State University

Rowan University

近二十年來,Rowan University 依靠 terasIC 為學生提供高質量的 FPGA 開發工具套件,以學習數字系統,計算機體系結構和嵌入式系統。 我在課程中一直要求我的學生使用 DE0-Nano ,DE0 和/或 DE10-Lite ,因為 terasIC 所提供的開發工具套件確實很有幫助,學生們在實驗室外也能夠繼續進行實驗。 我們對 terasIC 的產品,銷售和技術支持非常滿意,並將繼續使用 terasIC 開發套件。

|

Michael D Muhlbaier Instructor of Electrical and Computer Engineering Rowan University, New Jersey |

Stanford University

友晶科技協助我們打造最先進的 FPGA/SoC實驗室並且總是能及時的為我們提供專業幫助, 是一個非常出色的合作夥伴。我由衷感謝友晶科技提供給我們的一流品質及上等的服務!

史蒂文克拉克博士,

史丹佛大學電機工程系教學實驗室經理

University of Eastern Philippines

I am Engr. BLESS G. AMPUAN, currently working as Instructor in University of Eastern Philippines. I am honored and grateful to the Intel FPGA Academic Program through the Terasic, for donating DE10-Standard which will be utilized for instructional and research purposes. The boards were utilized by the electrical engineering students in their subjects ECE311 Logic Circuit and Switching Theory and ECE321 Microprocessor Systems. The FPGA is somehow new to us, at first we find it complicated but right we read the user manual, these boards are very helpful and interesting in school laboratory activities. My students are very enthusiastic to use the said boards. I highly recommend DE10-Standard because the board itself is so comprehensive and a very powerful electronic kit which can be used for school and research outputs. Thank you Terasic for this powerful FPGA boards.

|

Instructor: Engr. Bless G. Ampuan |

XINADIST

我在英特爾 FPGA 技術培訓合作夥伴 XINADIST 負責培訓、外包開發和諮詢。我經常看到許多研究人員和開發人員使用 Terasic 提供的電路板和文檔成功地執行了他們的項目。他們可以使用 Terasic 的評估板和最新的 FPGA(如 Stratix10、Arria10、MAX10)來縮短開發時間。

下面的照片展示了我們如何在韓國一所大學的教室中使用 DE1-SoC 板進行教育。 Terasic 板嵌入了 USB blaster I 或 II,您無需使用 JTAG 下載電纜。由於您可以輕鬆地將其連接到計算機並與 Quartus 一起操作電路板,因此您可以使用 Verilog-HDL 或 VHDL 快速建模和驗證操作。此外,使用 NiosII 和 RISC-V 等微處理器內核,您可以輕鬆驗證 IP。最後,您可以使用 Stratix、Arria 和 Cyclone V SoC 系列練習基於 linux 的操作系統移植、設備驅動程序和各種應用程序。

XINADIST

Aaron Yang principal engineer

您是否有使用 Terasic 產品或 Terasic Design 服務的豐富經驗?

請與我們分享 support@terasic.com

!